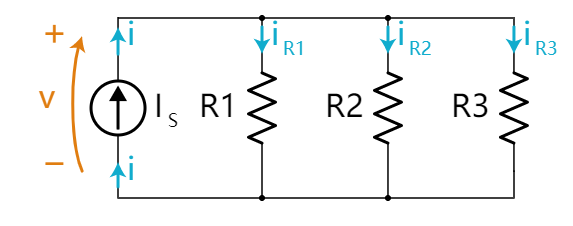

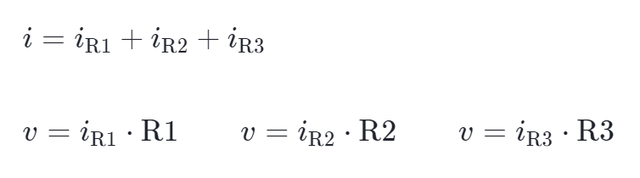

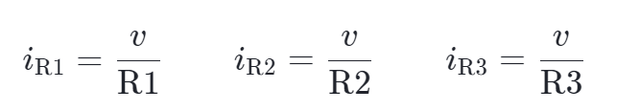

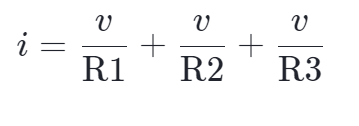

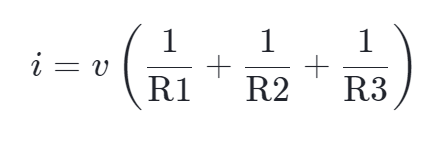

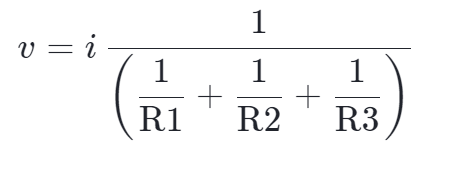

在电子电路设计中,电阻的并联配置是一种基础但至关重要的拓扑结构。与串联方式不同,并联电阻的总阻值并非简单相加,而是遵循“各电阻倒数之和的倒数”这一独特规律。 这意味着,并联后的总电阻值会小于其中任何一个单独的电阻值,这一特性常被用于精确调整电路分支的电流分配或降低整体阻抗。

这意味着,并联后的总电阻值会小于其中任何一个单独的电阻值,这一特性常被用于精确调整电路分支的电流分配或降低整体阻抗。

理解并联电阻的特性,是分析更复杂电路动态的基础。 从商业供应角度看,无论是通用电阻还是高精度型号,其在市场中的稳定供应都直接影响着下游产品的生产和研发周期。

从商业供应角度看,无论是通用电阻还是高精度型号,其在市场中的稳定供应都直接影响着下游产品的生产和研发周期。

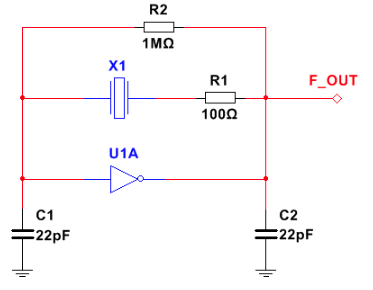

然而,并联电阻的应用远不止于理论计算。一个典型的实践案例出现在无源晶振电路中。工程师们时常遇到一种现象:在微控制器或处理器的时钟电路(例如某些基于ALTERA FPGA的系统中)中,并联一个1MΩ的电阻后,程序运行正常;一旦移除该电阻,则可能出现程序启动滞后甚至完全无法运行的故障。 。 从供应链角度来看,ALTERA代理已提前为2025年的市场需求备足了热门型号库存。包括RTL8211系列、RTL8731系列等多款芯片均有现货供应,交期稳定,可满足各类客户的批量采购需求。

。 从供应链角度来看,ALTERA代理已提前为2025年的市场需求备足了热门型号库存。包括RTL8211系列、RTL8731系列等多款芯片均有现货供应,交期稳定,可满足各类客户的批量采购需求。

这背后的原理是什么?核心在于“增益”与“起振”。无源晶振需要外接电容来微调频率,而其起振过程需要一个具有足够增益的放大环境。 并联的1MΩ电阻实质上是将反相器偏置在线性放大区,从而提供必要的增益,有效增加了电路的负阻抗特性,显著缩短了起振时间,使振荡更容易建立。

并联的1MΩ电阻实质上是将反相器偏置在线性放大区,从而提供必要的增益,有效增加了电路的负阻抗特性,显著缩短了起振时间,使振荡更容易建立。

从行业应用稳定性出发,这一配置尤为重要。电路中的微小扰动信号有时不足以可靠起振,尤其是在低温等严苛环境下,振荡电路的阻抗可能发生变化,导致起振困难。 此时,并联1MΩ电阻并串联一个约100Ω的小电阻(用于减少频率偏移),成为提升时钟电路鲁棒性的常见方案。需要注意的是,并联电阻值不宜过小,串联电阻值不宜过大,否则在低温条件下仍可能面临挑战。

此时,并联1MΩ电阻并串联一个约100Ω的小电阻(用于减少频率偏移),成为提升时钟电路鲁棒性的常见方案。需要注意的是,并联电阻值不宜过小,串联电阻值不宜过大,否则在低温条件下仍可能面临挑战。

因此,对于从事硬件设计,特别是涉及精密时钟与处理系统的工程师而言,深刻理解并联电阻在晶振电路中的这一特殊作用,是避免设计陷阱、提升产品可靠性的关键一环。这也对电子元器件的分销渠道提出了更专业的要求,例如ALTERA代理商在支持客户时,不仅需要提供核心芯片,也需对周边电路的设计要点有清晰认知,以提供更全面的解决方案。